58

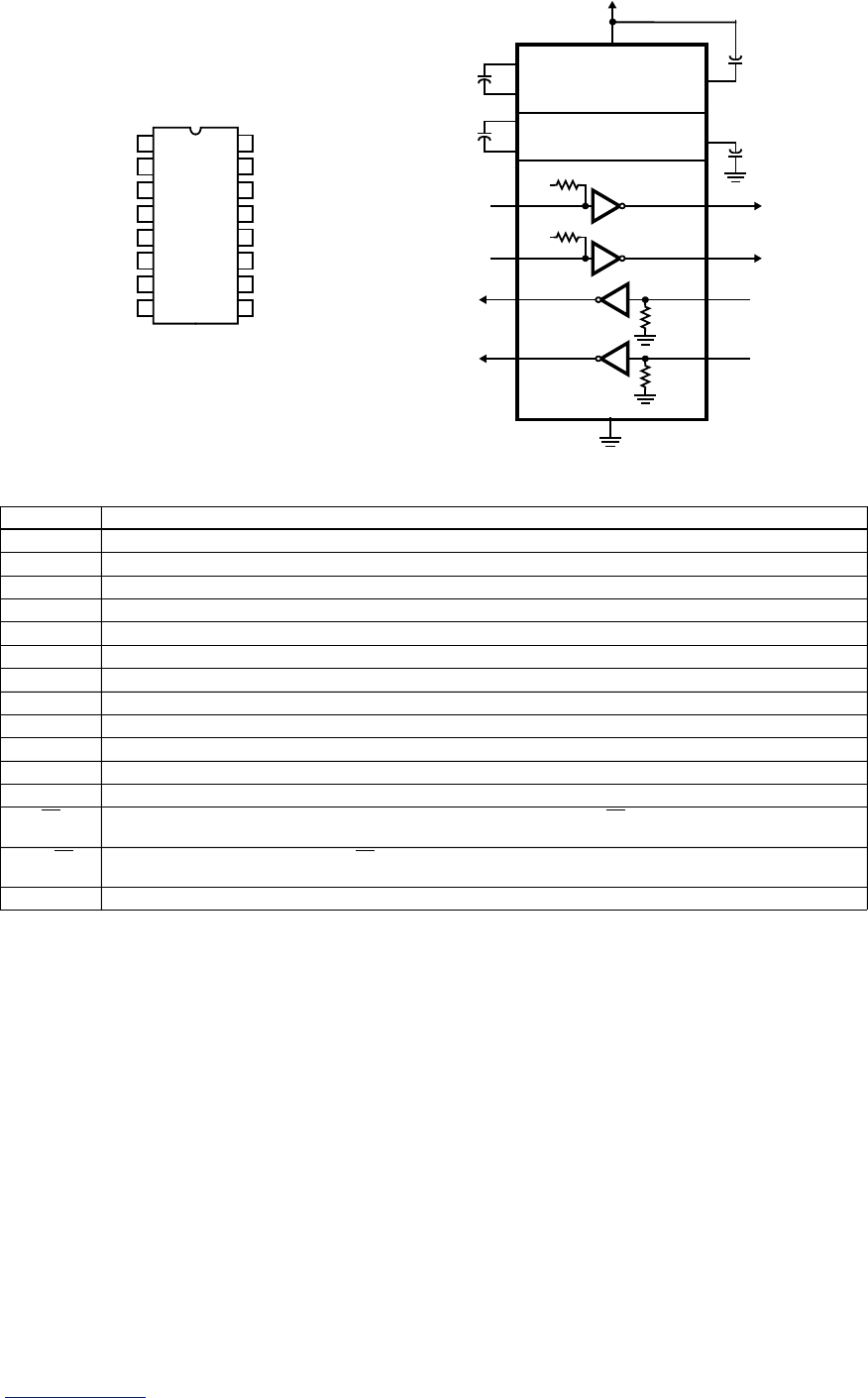

HIN202E (PDIP, SOIC)

TOP VIEW

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

C1+

V+

C1-

C2+

C2-

R2

IN

T2

OUT

V

CC

T1

OUT

R1

IN

R1

OUT

T1

IN

T2

IN

R2

OUT

GND

V-

V

CC

+5V

2

V+

16

T1

OUT

T2

OUT

T1

IN

T2

IN

T1

T2

11

10

14

7

+5V

400k

+5V

400k

R1

OUT

R1

IN

R1

1312

5k

R2

OUT

R2

IN

R2

89

5k

+10V TO -10V

VOLTAGE INVERTER

0.1 F

6

V-

C2+

C2-

+

0.1 F

4

5

+5V TO 10V

VOLTAGE INVERTER

C1+

C1-

+

0.1 F

1

3

+

0.1 F

+

GND

15

Pin Descriptions

Pin Assignment

PIN FUNCTION

V

CC

Power Supply Input 5V 10%, (5V 5% HIN207E).

V+ Internally generated positive supply (+10V nominal).

V- Internally generated negative supply (-10V nominal).

GND Ground Lead. Connect to 0V.

C1+ External capacitor (+ terminal) is connected to this lead.

C1- External capacitor (- terminal) is connected to this lead.

C2+ External capacitor (+ terminal) is connected to this lead.

C2- External capacitor (- terminal) is connected to this lead.

T

IN

Transmitter Inputs. These leads accept TTL/CMOS levels. An internal 400k pull-up resistor to V

CC

is connected to each lead.

T

OUT

Transmitter Outputs. These are RS-232 levels (nominally 10V).

R

IN

Receiver Inputs. These inputs accept RS-232 input levels. An internal 5k pull-down resistor to GND is connected to each input.

R

OUT

Receiver Outputs. These are TTL/CMOS levels.

EN Enable Input. This is an active low input which enables the receiver outputs. With EN = 5V, the outputs are placed in a high

impedance state.

SD,

SD Shutdown Input. With SD = 5V (HIN213E SD = 0V), the charge pump is disabled, the receiver outputs are in a high impedance

state (except R4 and R5 of HIN241E) and the transmitters are shut off.

NC No Connect. No connections are made to these leads.

QU50 : HIN202ECB